Recent Developments in Electronics and Communication Systems KVS Ramachandra Murthy et al. (Eds.) © 2023 The authors and IOS Press. This article is published online with Open Access by IOS Press and distributed under the terms of the Creative Commons Attribution Non-Commercial License 4.0 (CC BY-NC 4.0). doi:10.3233/ATDE221235

# Comparative Analysis of Approximate Integer and Floating-Point Multiplier

P. Yuvasri Lakshmi<sup>a</sup>, Y. Lavanya<sup>b</sup>, B. Jagadeesh Babu<sup>c,1</sup>, B. S. Sridevi<sup>d</sup>

<sup>*a,b,c*</sup>Department of ECE, Aditya College of Engineering, Surampalem, India <sup>*d*</sup>Department of ECE, Aditya Engineering College, Surampalem, India

**Abstract.** The approximate multipliers allow saving power and area by deploying many other contemporary, error flexible, compute intensive application. In this manuscript, first discussed an original minimally biased approximate integer multiplier design method that can be configured with an error. The proposed MBM architecture by combining by an approximated 'Log' biased numeral multiplier of a specific error reduction mechanism. After that analysed a place of original estimated floating point (FP) multiplier. These are showing to facilitate these FP multipliers is on the Pareto obverse on the region designs space against power and error. Here used the 45-nm criterion cell library to synthesis the designs. When compared to the precise version we designed MBM integer offers 84% power reduction and 78% area reduction. The proposed estimated FP multiplier offers 57% power and 25% area improvements. It is smaller amount of 4% error bias, 8% mean error and 28% of peak error.

Keywords: Approximate integer, Multiplier, Floating point, Computing, Power reduction

## 1. Introduction

Approximate computing is mainly used to decrease the gaps between the computing requirements and available processing resources. People who search or shown that highly compute-intensive are called error-resilient Example: multimedia processing and machine learning [1]. These applications to allow the existence of computational errors with the decline to low in the output feature. Unnatural error is allowed to develop these applications to achieve an easier and important system with the decline to low final output feature. These consist of a small number of dominated Kernels which related closely to multiplication [2], [3]. FP multipliers have to collect comparatively small observations for approximation than their integer equivalent FP multiplier are advisable in computing system due to the below conditions [4]. Approximate multipliers are large, thick in design space and it is popular. Which is offers a different off against source important arrangement as well as a compression [4], [5]. Hardware multipliers are two types 1. Integer multipliers. 2. FP multipliers in this paper a novel fault configurable modestly influenced approximate unsigned integer multiplier and number of approximation FP multiplier [6]. The advanced MBM multipliers are constructed to have very little error bias. Here shown that analysed error configuration MBM multiplier

<sup>&</sup>lt;sup>1</sup>Corresponding Author, B. Jagadeesh Babu, Department of ECE, Aditya College of Engineering, Surampalem, A.P., India, India; E-mail: jagadeesh\_ece@acoe.edu.in

produces favourable designed point in the against error. The area against fault places of condition is the art of estimated integer multiplier [7], [8], [9].

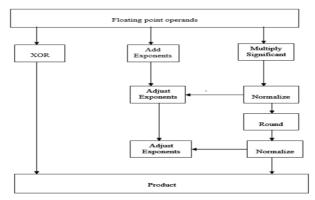

It is relatively less precise and helpful to invent resource proficient FP multiplier shown in figure 1. In this, used the best type of the advanced MBM in FP multiplier. It is used to generate a huge and thick design space [10, 19].

Figure 1. Example of MBM multiplier

FP multiplier recommended more than 50\*power development and other than 25\*area improvement concerning IEEE-75. A single accuracy FP multiplier by means of a mean error  $\leq$  5%. FP multipliers are used in the field of multimedia dispensation and learning mechanism [8]. Embedded and computing systems are needed to work some digital signal processing and to divide the applications. To improve energy-efficient of working such applications [10, 11].

### 2. Related Works

In resents years using binary logarithms performance a multiplication and division in computers. Multiplication and division operation in the computer is usually accomplished by a series of additions, subtraction and shifts without using table looksups. Using this logarithm is to increase the speed of operation [1, 11]. The using a representation of bit width FP data reducing the FP power consumption. This FP bandwidth reduces energy savings using variable bandwidth FP unit. From this experiment show that up to 66% reduction in multiplier [2, ,12 14]. In 2012 proposed a new system for working of approximate programming. It provides an extension operation and storage which save energy and cost accuracy. And then proposed a truffle which is a dual voltage micro for working approximation. High voltage for specific operation and estimated operation. It is evaluated numerous applications and reveal energy savings of up to 43% [3, 11]. In 2013 designed an application pliability characterization frame work analysis and characterization of flexibility [13, 18]. And then applications of resilience characterization [14, 15, 16]. Here performed experiments to explain the association between the inherent buoyancy and different applications characteristics such as computation patterns, the scale of input data, quality metric etc [17]. A multiplier which reduces the energy efficiency of multiplication and performed a matrix multiplication when compared to the precise multiplier and their applications. Compare with a specific

multiplier that projected multiplier can consume 56% less power. This improves the area efficiency and energy [18]. In this to full gaps of decreasing benefits from technology and to improve the performance of computing efficiency then involve the techniques and applications of approximate computing [19]. In 2016, it is proposed different methods for estimated computed using AC. Finding the strategy for approximate program portion and monitor the output excellence and classifies techniques based on AC. Finally, this article provides insight to researches into functioning of AC technique [11]. In 2017 In previous a lot of technique for estimated computing technique that proposed by dissimilar types of the scheme stacks commencing circuit to structural design to software. In this manuscript designed a new quantized table lookup (QLUT). It is used for approximate the Meta function used in the centre computing. The construction of the QLUT is made possible by input quantization. It was for that devised to reduce the energy savings of 46% [14, 11]. In year 2020 first proposed an original simply influenced estimated integer multiplier design that can be configured with an error. The proposed MBM architecture by combining with an estimated 'Log' biased numeral multiplier a specific error reduction mechanism. After that it was proposing a position of novel estimated FP multiplier. That was shown these FP multipliers are on the Pareto-front on the region designs space against power versus error. Here used the TSMC 55-nm standard cell records to synthesis the design [19].

#### 3. Methodology for Approximate of Integer multiplier

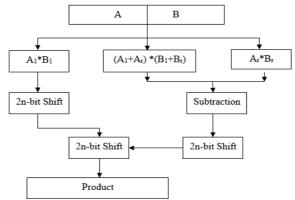

In the literature work, prior work related to approximate integer multiplier designs regard particular sequence similar multiplier as the basic design used for approximation. Here design is used that consisting of approximately 22 blocks of multiplier used to construct multiplier. The multipliers required an estimate of the biased artefact growth shown in figure 2.

Figure 2. Block diagram of floating-point multiplier

These multipliers are used to determine the location of the most important one in the operand. In higher bit of the contribution, operand is sent to a reproduction component and minor bits send to a non-duplication. In an m-bit fragment it is extract from every n-bit input operand. The extracted m-segment may start at two fixed positions. The remaining bits are shortened. This version allows three starting positions. The design is

parallel to the SSM design. The LSB of every of the extract k-bit section is place to 1 shown in figure 2. The process of the logarithm simplifies an addition to multiplication. It requires a log and antilog. The most resource-efficient is the linear rough calculation-based techniques that are Mitchell techniques. Mitchell projected to calculate estimated binary log and anti-log by linear similar to the antilog-log curve every power of two interval. The approximate 'log' standards of the two operands are supplementary to that number obtain the approximate value the repeal of this 'log' calculation process is applied shown in figure 2.

Consider an N-bit unspecified integer with 'B' bits, then can B have represented as:

$$B = \sum_{i=0}^{N-1} 2^{i}$$

(1)

'B' can write as:

$$B = 2^{k} (1 + \sum_{i=0}^{K-1} 2^{i-k} b_{i})$$

(2)

This equation can be written as:

$$B = 2^{k}(1+x).$$

(3)

The accurate binary log of 'B' is .:

$$\log_2 \mathbf{B} = \mathbf{K} + \log_2(1+\mathbf{x}) \tag{4}$$

#### 4. Results and evaluation of MBM integer multiplier

To demonstrate the utility of the projected MBM multiplier, here evaluate the propose error and metrics. Besides that, it is also shown the efficiency of the projected inaccuracy diminution method. The error diminution term projected by 'Siferd and Abed' for 'log' and 'antilog' inaccuracy reduction is the simplest to implement in hardware. In conditions of the previous two faults metric (peak error and mean) is proposed MBM multiplier. Thought at the expense of table 1 and table 2. For the 16 bit implies the overhead reduction function in the MBM multiplier. Its area reduction concerning the accurate multiplier is 3.8% and the energy utilization is still superior to the precise multiplier.

Table 1. Design and error metrics for MBM multiplier: Multiplier size N=8 Bits

|            |                  |       | Munuph        | er size n=o n | 115          |              |           |

|------------|------------------|-------|---------------|---------------|--------------|--------------|-----------|

| Multiplier |                  | D     | esign metri   |               | Error matrix |              |           |

|            | Reduction<br>(%) |       | Actual Value  |               | Bias         | Mean         | Peak      |

|            | Area             | Power | Area<br>(μm²) | Power<br>(mw) | Error<br>(%) | Error<br>(%) | Error (%) |

| MA         | -                | -     | 448.0         | 36.8          | -            | -            | -         |

| AXM        | 35.46            | 39.80 | 289           | 22.5          | 0.05         | 2.79         | 7.82      |

| MBM        | 3.8              | 18.52 | 429.2         | 41.7          | -0.69        | 1.31         | 14.39     |

| Accurate   | 40               | 18    | 231.6         | 17.0          | -3.86        | 3.96         | 11.21     |

| Multiplier   |               | De    | sign metrics  | Error matrix  |              |              |              |

|--------------|---------------|-------|---------------|---------------|--------------|--------------|--------------|

|              | Reduction (%) |       | Actual Value  |               | Bias         | Mean         | Peak         |

|              | Area          | Power | Area<br>(μm²) | Power<br>(mw) | Error<br>(%) | Error<br>(%) | Error<br>(%) |

| Accurate     | -             | -     | 190.9         | 188.2         | -            | -            | -            |

| MBM          | 64.9          | 73.8  | 687.3         | 48.9          | -0.08        | 2.68         | 8.81         |

| MBM-8        | 67            | 76.6  | 648           | 43.9          | -0.07        | 2.68         | 8.82         |

| <b>MBM-7</b> | 68.6          | 77.8  | 636.3         | 41.3          | -0.09        | 2.48         | 7.83         |

| MBM-6        | 68.5          | 77.6  | 618.4         | 42.3          | -0.08        | 2.78         | 6.86         |

| MBM-5        | 67.6          | 78    | 598.2         | 38.3          | -0.07        | 2.68         | 8.9          |

| MBM-4        | 70            | 81.4  | 585.9         | 35.7          | -0.09        | 2.98         | 8.8          |

| MBM-3        | 71.7          | 82.5  | 557.1         | 33.9          | -0.08        | 2.64         | 8.29         |

| MBM-2        | 72.9          | 83.7  | 536.1         | 31.6          | -0.07        | 2.44         | 8.48         |

| MBM-1        | 76            | 82.3  | 477.1         | 28.7          | -0.08        | 2.63         | 9.26         |

Table 2. Design and error metrics for MBM multiplier: Multiplier size N=16 Bits

The configured MA-based is most efficient resource multiplier but the most errorfree. This indicates 19.2 % power improvement and 13.6 % area improvement compared to the FMP-R comparison. the configured AFMB based on MBM also shows a considerable improvement in power and area. The implementation on base models of the error configuration system as generates various error-are and error-power trade-offs.

## 5. Conclusion

In this manuscript it is discussed using the MBM and other estimated integer multipliers for a range of estimated FP multiplier. First introduce a new optimisation method for the approximate integer multiplier to construct this FP multiplier. The planned approximate FP multiplier offers better fault efficiency then the precise scaling. The proposed FP multiplier offers 28\* area improvement and 58\*power. It is less than 4% error bias, 7% mean error and 25% peak error. After that it is discussed a set of novel estimated FP multiplier. These are showing that these FP multiplier on the Pareto front on the area designs. The power versus error and space versus error are also discussed. Here used the TSMC 55-nm pattern cell collection to mixture the design.

## References

- Mitchell JN. Computer multiplication and division using binary logarithms. IRE Transactions on Electronic Computers. 1962 Aug (4):512-7.

- [2] Tong JY, Nagle D, Rutenbar RA. Reducing power by optimizing the necessary precision/range of floating-point arithmetic. IEEE Transactions on Very Large-Scale Integration (VLSI) Systems. 2000 Jun;8(3):273-86.

- [3] Nimmakayala S, Mummidi B, Kunda P, Kumar S. Modern Health Monitoring System Using IoT. In ICCCE 2020 2021 (pp. 1135-1144). Springer, Singapore.

- [4] Kulkarni P, Gupta P, Ercegovac M. Trading accuracy for power with an under designed multiplier architecture. In2011 24th International Conference on VLSI Design 2011 Jan 2 (pp. 346-351). IEEE.

- [5] Brundana MS, Rajeswari PS, Sravani N, Kumar S. Successive Approximation Compressor for Efficient FIR Filters in C-MOS VLSI Design. In2021 6th International Conference for Convergence in Technology (I2CT) 2021 Apr 2 (pp. 1-4). IEEE.

- [6] Esmaeilzadeh H, Sampson A, Ceze L, Burger D. Architecture support for disciplined approximate programming. InProceedings of the seventeenth international conference on Architectural Support for Programming Languages and Operating Systems 2012 Mar 3 (pp. 301-312).

- [7] Chippa VK, Chakradhar ST, Roy K, Raghunathan A. Analysis and characterization of inherent application resilience for approximate computing. InProceedings of the 50th Annual Design Automation Conference 2013 May 29 (pp. 1-9).

- [8] Siddiqa, S. H. M., Apurva, K., Nandan, D., & Kumar, S. (2021). Documentation on Smart Home Monitoring Using Internet of Things. In *ICCCE 2020* (pp. 1115-1124). Springer, Singapore.

- [9] Singh M, Nandan D, Kumar S. Statistical Analysis of Lower and Raised Pitch Voice Signal and Its Efficiency Calculation. Traitement du Signal. 2019 Oct 1;36(5):455-61.

- [10] Nandan D, Kanungo J, Mahajan A. An efficient VLSI architecture design for logarithmic multiplication by using the improved operand decomposition. Integration. 2017 Jun 1; 58:134-41.

- [11] Venkata Dharani, B., Joseph, S.M., Kumar, S. and Nandan, D., 2021. Booth Multiplier: The Systematic Study. *ICCCE 2020*, pp.943-956.

- [12] Singh, M. K., Singh, A. K., & Singh, N. (2019). Multimedia analysis for disguised voice and classification efficiency. *Multimedia Tools and Applications*, 78(20), 29395-29411.

- [13] Singh MK, Singh N, Singh AK. Speaker's voice characteristics and similarity measurement using Euclidean distances. In2019 International Conference on Signal Processing and Communication (ICSC) 2019 Mar 7 (pp. 317-322). IEEE.

- [14] Punyavathi G, Neeladri M, Singh MK. Vehicle tracking and detection techniques using IoT. Materials Today: Proceedings. 2022 Jan 1; 51:909-13.

- [15] Veerendra G, Swaroop R, Dattu DS, Jyothi CA, Singh MK. Detecting plant Diseases, quantifying and classifying digital image processing techniques. Materials Today: Proceedings. 2022 Jan 1; 51:837-41.

- [16] Padma U, Jagadish S, Singh MK. Recognition of plant's leaf infection by image processing approach. Materials Today: Proceedings. 2022 Jan 1; 51:914-7.

- [17] Nandini A, Kumar RA, Singh MK. Circuits Based on the Memristor for Fundamental Operations. In2021 6th International Conference on Signal Processing, Computing and Control (ISPCC) 2021 Oct 7 (pp. 251-255). IEEE.

- [18] Anushka RL, Jagadish S, Satyanarayana V, Singh MK. Lens less Cameras for Face Detection and Verification. In2021 6th International Conference on Signal Processing, Computing and Control (ISPCC) 2021 Oct 7 (pp. 242-246). IEEE.

- [19] Kumar S, Nandan D, Singh MK, Kumar R. A multiple band-notched monopole antenna with incorporated GSM and UWB for wireless applications. Inter. J. Adv. Sci. Technol. 2019 Nov;28(16):362-78.