Transdisciplinarity and the Future of Engineering B.R. Moser et al. (Eds.) © 2022 The authors and IOS Press. This article is published online with Open Access by IOS Press and distributed under the terms of the Creative Commons Attribution Non-Commercial License 4.0 (CC BY-NC 4.0). doi:10.3233/ATDE220633

# Integrated Patent Landscape Analysis Based on Semiconductor Infringement Landmark Cases

C.H. CHIEN<sup>1</sup>, Kevin L.K. Tu<sup>2</sup>, H.J. LIN and A.J.C. TRAPPEY Department of Industrial Engineering and Engineering Management, National Tsing Hua University, Hsinchu, Taiwan

> Abstract. This research conducts integrated patent landscape analyses based on the landmark cases of patent infringement disputes between VLSI Technology and Intel. Complex multidisciplinary semiconductor knowledge ontology and taxonomy are derived from the landmark cases. Since Intellectual property (IP) and patent legal right protections defensively and offensively are critically important to high-tech companies for remaining globally competitive, the analysis of the patent portfolio consisting of the multiple technology innovations is the major challenge of this research. First, the patent search based on keywords of the patents under dispute. Afterward, the patenting trends of top assignees in the semiconductor industry, ranked in top International Patent Classification (IPC) codes, are analyzed. Further, this research performs topic clustering, a form of non-supervised learning, to divide all domain patents into unique topic groups. The ontology schema, based on the topic clustering results, builds the critical domain knowledge map, which can be used to highlight transdisciplinary technologies and their IPs. The research ensures newly granted patents, which focus on the disputed technical topics with literally or equally similar claims, must be cautious about the rist of potential infringement disputes. In the future, this transdisciplinary approach can be applied to various industries for IP protection.

> Keywords. patent mining, non-practicing entity (NPE), K-means, Latent Dirichlet Allocation (LDA), knowledge ontology

# Introduction

VLSI Technology, Inc is known as the pioneer of application-specific integrated circuit (ASIC) technology. The VLSI name is taken from the acronym Very Large Scale Integration. In the early years, semiconductors evolved from small-scale integration (SSI), medium-scale integration (MSI), large-scale integration (LSI), and finally developed to VLSI. VLSI Technology, Inc utilized its software design technology to assist semiconductor manufacturers with the development and production of advanced integrated circuits. VLSI also had an innovative system that could effectively design and customize its chips. The invention was introduced to emerging markets in the 1980s and helped VLSI increase its revenue from less than US\$20 million to more than US\$100 million in four years [1].

<sup>&</sup>lt;sup>1</sup> Corresponding Author, Mail: s109034852@m109.nthu.edu.tw.

<sup>&</sup>lt;sup>2</sup> Corresponding Author: Mail: s110034607@m110.nthu.edu.tw.

At the beginning of April 2019, VLSI Technology LLC sued Intel for infringing on three patents. In March 2021, the District Court of the Western District of Texas ruled that Intel had infringed two of the patents owned by VLSI Technology LLC and required US\$2.175 billion of damages. The two patents were U.S. patent number 7523373 for minimum memory operating voltage technique and U.S. patent number 7725759 for system and method of managing clock speed in an electronic device. Intel had to pay US\$1.5 billion and US\$675 million respectively. In the process of seeking a retrial, Intel asserted that the jury's evidence and verdict were wrong. In addition, there was also a patent infringement lawsuit between VLSI and Intel. On April 21, another jury of the Waco court ruled that Intel had defeated the US\$3.1 billion patent trial.

This research focused on the two related patents at first. The analysis on them would be conducted separately to assess different companies in the industry based on their competitive technologies. Furthermore, Patent search results would be grouped by clustering methods. The ontology would also be built based on the keyterms and topics of each cluster. In the end, this research aims to find patents in each group that does not cite the related two patents.

#### 1. Methodology

This section will introduce the methodology of the patent analysis. In section 2.1, the patent search strategy is presented and the search keyword is shown. Section 2.2 includes the patent analysis techniques such as K-means and LDA topic modeling. This research would further use these techniques to do clustering.

#### 1.1. Patents Search Strategy

In this research, the patents search is conducted by Derwent Innovation. This is a famous and powerful patent retrieval tool that can greatly reduce users' time by providing exclusive Derwent-made titles and abstracts. Because the patent infringement lawsuit is related to two patents, we would look into the infringement claims and then derive related key components for the search query. A key component is defined as the same keyword shown after the article "a" and "the." First of all, the first patent number is US7523373B2, and the title is "Minimum memory operating voltage technique." Search keywords are shown in Table 1. We retrieved a total of 443 patents based on the search query.

| Table 1. US7523373B2 patents search query keyword. |                                                                 |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------------|--|--|--|

| US7523373B2                                        |                                                                 |  |  |  |

|                                                    | "integrated circuit" or "memory" or "minimum operating voltage" |  |  |  |

| <b>T</b> •                                         | "functional circuit" or "non-volatile memory (NVM) location"    |  |  |  |

| Торіс                                              | "regulated voltage" or "signal" or "controller" or "processor"  |  |  |  |

|                                                    | "voltage regulator" or "power supply selector"                  |  |  |  |

Our second patent number is US7725759B2, and the title is "System and Method of Managing Clock Speed in an Electronic Device." Our search keyword is shown in Table 2. We retrieved a total of 946 patents based on the search query.

|       | Table 2. US7725759B2 patents search query keyword.                  |

|-------|---------------------------------------------------------------------|

|       | US7523373B2                                                         |

|       | "bus" or "variable clock frequency" or "master device" or "request" |

| - ·   | "high-speed clock" or "predefined change"                           |

| Торіс | "programmable clock controller" or "embedded computer program"      |

|       | "clock frequency" or "arbiter" or "clock controller"                |

# 1.2. Patent Clustering

Clustering is a data mining method used to separate a heterogeneous population into several homogeneous subgroups without predefined classes [2]. Clustering algorithms have various types that can be classified into two different categories, namely, partitional and hierarchical. The partitional type has many different kinds, one of which is called the K-means, which uses a centroid-based technique. K-means is a typical clustering algorithm in data mining and is widely used for clustering large sets of data. In 1967, MacQueen firstly proposed the k-means algorithm, which was one of the most simple, non-supervised learning algorithms, which was applied to solve the problem of the wellknown cluster [3]. K-means clustering algorithm classifies a large number of patents into several groups. Each group represents its theme so that it's easier to identify what the patent is about. "K" indicates the number of clusters that the user designates, and "means" indicates the center of each cluster. We can determine the number of clusters and distinguish different topics of patents.

# 1.3. Latent Dirichelet Allocation (LDA) Topic Modeling

There are so many words in a document and it may be hard for people to read it quickly. LDA algorithm classifies the words into different groups, and each group represents a topic. That is to say, a document may contain many topics and each topic has some words that we can see in the document frequently. LDA algorithm enables us to take a brief look at those topics and some top keywords in each topic. It's easier for us to identify the key points of each document.

#### 2. US7523373B2 (Minimum memory operating voltage technique)

In this chapter, we took a broader perspective to look into the patent search results related to US7523373B2 and find the patent application trends according to different IPC codes and top 5 assignees. At last, Radar analysis for top 5 assignees on top 5 IPC codes is also done for the evaluation of the main strength of each company.

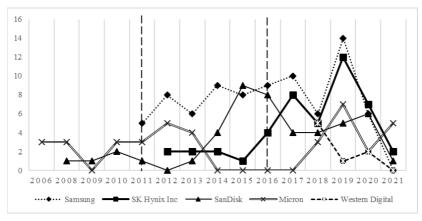

Figure 1. Minimum memory operating voltage technique patent application trends.

The minimum memory operating voltage technique patent application trends of the top 5 assignees are Samsung, SK Hynix Inc, SanDisk, Micron, and Western Digital. The first patent US7523373B2 was filed in 2006. As a result, this research divides the timeline into three sections: 2006 to 2011, 2011 to 2016, 2016 to 2021 are shown in Figure 1.

There are only two assignees, SanDisk and Micron, who had patent applications within the first five years. Micron had more patents than SanDisk during this timeframe. From 2011 to 2016, Samsung and SK Hynix Inc had started to apply for their patents. SanDisk had increasing patent application trends and reached its peak while Micron had started to decrease its patent applications to zero. Although Samsung had just started to apply for patents, Samsung had the most patents during this timeframe. From 2016 to 2021, Samsung, SK Hynix Inc, and Micron had increasing patent application trends at first and even reached their peak in 2019.SanDisk did not apply for as many patents as before. Western Digital is an emerging assignee that had started to apply for patents in 2018. However, because of COVID-19, all assignees had a decline in patent application trends since 2019.

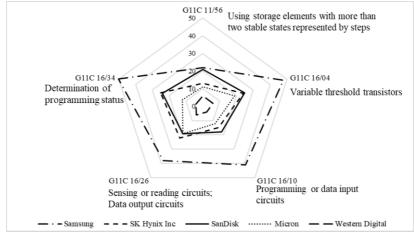

Figure 2. Minimum memory operating voltage technique radar chart competitor analysis.

The top IPCs are G11C 16/04, G11C 16/34, G11C 16/26, G11C 16/10, and G11C 11/56. This research chooses the top 5 assignees, Samsung, SK Hynix Inc, Sandisk, Micron, and Western Digital to perform radar analysis. The results are shown in Figure 2, and the scales of the plot represent the number of patents owned by different assignees. Samsung owns the most patents, which is more dominated than others. The results showed that Samsung's and SK Hynix Inc's main technique is about "the determination of programming status." SanDisk's main technique is "using variable threshold transistors," Micron's main techniques are "using variable threshold transistors," sensing or reading circuits" or "data output circuits." The technical fields of Western Digital are more evenly distributed. Western Digital has 6 patents for "using storage elements with more than two stable states represented by steps," 6 patents for "using variable threshold transistors," and 6 patents for "sensing or reading circuits" or "data output circuits."

# 3. US7725759B2 (System and Method of Managing Clock Speed in an Electronic Device)

In this chapter, we took a broader perspective to look into the patent search results related to US7725759B2 and find the patent publishing trends according to different IPC codes and top 5 assignees. At last, Radar analysis for top 5 assignees on top 5 IPC codes is also done for the evaluation of the main strength of each company.

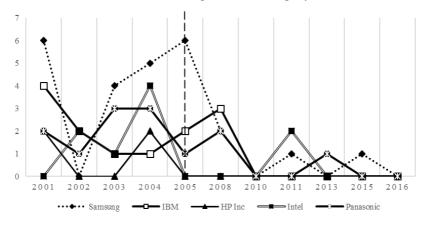

Figure 3. Patents publishing trends - related to system and method of managing clock speed in an electronic device.

The "System and Method of Managing Clock Speed in an Electronic Device" related patent applications are filed mostly by 5 assignees, i.e., Samsung, IBM, HP Inc, Intel, and Panasonic. The infringement lawsuit (related to patent US7725759B2) was filed in 2005. Before that, as shown in Fig. 3, these assignees had applied for more relevant patents. Samsung had the most patents and had reached its peak in 2005, but the number of patents started to decrease since then. IBM also had quite a lot of patents but it did not apply for patents anymore after 2010. The number of patents of HP Inc was relatively few and HP stopped applying after 2005. Intel had more patents from 2002 to 2004, and it had become silent from 2005 to 2010. In 2011, Intel applied for two patents. As for Panasonic, it had more patents from 2001 to 2008, and it had only applied for one patent in 2013. Panasonic did not apply for any patent afterward.

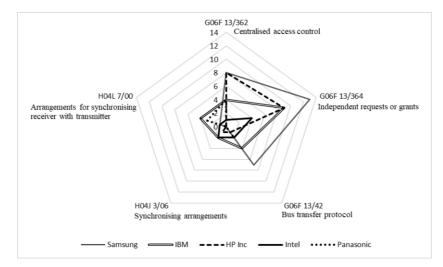

There are no patent being applied after 2015. We can infer that these assignees do not have new invention in this field for some time. As a result, the techniques related to the second infringement case are matured and the industry did not pay more attention in R&D anymore. Further, the top IPCs, the majority of related patents fall under, are G06F 13/362, G06F 13/364, G06F 13/42, H04L 7/00, and H04J 3/06. The leading five assignees, i.e., Samsung, IBM, HP Inc, Intel, and Panasonic, and their patent portfolios are compared using the radar analysis as shown in Figure 4. The scales of the plot are the numbers of patents owned by different assignees. We can see that most techniques are under the IPC category defined as "G06F 13/364 - *electric digital data processing - interconnection of information or signals between memories, input/output devices or CPUs using independent requests or grants*", where specifically Samsung owns the most patents in this category. Overall, Samsung dominates the related IP landscape than leading patent assignees.

Figure 4. The radar char of top assignees' patent counts related to "system and method of managing clock speed in an electronic device".

### 4. K-means clustering, LDA, and ontology

In this chapter, we shifted our focus from macro to micro. We combine two patent search results into one cluster and conduct a detailed analysis on the cluster patents. We would then separate the cluster into numerous groups based on each characteristic and topic. The patent clustering and topic clustering results would then be organized into an ontology for easily identifying different technology techniques clusters in the future. In the end, we would find out the non-citation patents from each topic cluster and the assignees of these patents could be aware of and be prepared for future infringement cases.

# 4.1. K-means clustering and key term extraction

To categorize numerous patents into separate groups for better micro analysis of each patent, we performed k-means clustering algorithm and divided patents search results into three groups based on the distinguishment of the keyterm in each cluster. According

to the clustering results, a total of 1389 patents are divided into 450, 651, and 288 patents respectively. Partial clustering results are shown in Table 3. After dividing numerous patents into three clusters, we then perform keyterm extraction from each cluster. The keyterms are selected by meaningful terms in semiconductor industry.

| Cluster No. | <b>Cluster features</b> | Representative phrases                                                                                           |  |

|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------|--|

| 1           | memory                  | volatile/non-volatile, threshold, read operation, pas voltage regulator, nand string, access memory, float gate  |  |

| 2           | clock                   | clock signal, master clock, slave clock, clock frequency, clock generator, phase difference, synchronize, signal |  |

| 3           | bus                     | bus master, bus arbiter, request, bus clock, couple bus, peripheral bus, information processing                  |  |

| Table 3. | The | partial | clustering | result. |

|----------|-----|---------|------------|---------|

|----------|-----|---------|------------|---------|

# 4.2. LDA

Since every cluster has diverse representative phrases, it is best to divide each cluster into topic clusters. After several trials, two topics for each cluster are the best results. We also list some representative patents for each topic under the patent clusters for further patent analysis is shown in Table 4. Semiconductor background knowledge is also considered during the topic clustering to make reasonable categorization of each cluster.

|            | <b>T</b> •    | ¥7 1                                          | <b>D</b>              |

|------------|---------------|-----------------------------------------------|-----------------------|

| Sub-domain | Торіс         | Keyphrase                                     | Representative patent |

|            | Operation     | command, threshold,                           | KR1736457B1           |

|            |               | write, request, page,                         | US10949119B2          |

| Cluster 1  | ×             | configure, read                               | US9640263B2           |

| Memory     |               | transistor, layer,                            | US7523373B2           |

|            | Component     | terminal, capacitor,                          | US20030146454A1       |

|            | •             | substrate, mos, regulator                     | US7002869B2           |

|            |               | CPU, pulse, rate, oscillator, flip-flop       | US20090167375A1       |

|            | Application   |                                               | US7707450B1           |

| Cluster 2  | . ippirounion |                                               | US6279058B1           |

| Clock      | Communication | wireless, network, pwm,                       | US20030012158A1       |

|            |               | port, receiver, send,                         | US20020015423A1       |

|            |               | station                                       | WO2002001775A1        |

|            | Technique     | transfer, slave,<br>arbitration, grant, cycle | US7725759B2           |

|            |               |                                               | WO1991016680A1        |

| Cluster 3  |               |                                               | WO2005119465A1        |

| Bus        |               | CDI and a data t                              | US20170286358A1       |

|            | Structure     | SPI, serial, node, slot,                      | EP1014273A2           |

|            |               | transceiver, adapter                          | EP1505784A1           |

Table 4. The LDA-based outputs under the domain of the semiconductor industry.

# 4.3. Ontology construction

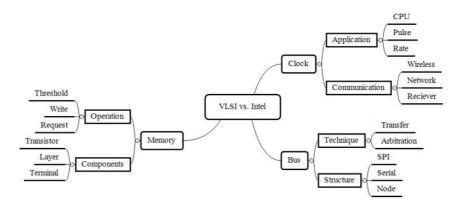

In this section, the ontology map of the VLSI vs. Intel infringement case is completed based on the previous outputs along with the help of transdisciplinary knowledge. The result is shown in Figure 5. A four-level ontology map has a hierarchical structure that includes domains, sub-domains, key topics, and key phrases from top to the bottom.

Figure 5. The semiconductor industry ontology output.

The patent search result related to the infringement case has three topics including the clock, bus, and memory. Patent US7523373B2 is related to the minimum operating voltage, memory, SRAM, and integrated circuit. Patent US7725759B2 is related to clock speed, a master device, bus, etc.

### 4.4. Non-citation patent results

This section finds out patents that do not cite patents at dispute. Since this research had divided the patent search results into six groups based on the characteristic of each topic, the non-citation patents would be categorized into six groups as well. This research selects the results of the non-citation patents according to the highest score of the combined patent impact index. The non-citation patents of cluster 1, cluster 2, and cluster 3 are shown in the following tables. This research also collects the DWPI title of non-citation patents.

The non-citation patents of cluster 1 are shown in Table 5. The assignees of these patents are almost the same as the top 5 assignees from the previous chapter. There is one more assignee named Qorvo. This company specialized in designing and manufacturing radio-frequency systems for wireless and broadband communication. Judging from the combined patent impact index, CN103730166B has the highest score. This patent claims a memory unit in a solid-state memory device of analog sensing, and this memory unit has a certain response when the threshold voltage is reached.

|                              | 1                                                |                                                           |                                                     |                                                    |

|------------------------------|--------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|

|                              | US11031085B2                                     | US20050047226A1                                           | CN103730166B                                        | CN113223586A                                       |

| Application<br>Date          | 2020/6/09                                        | 2014/7/16                                                 | 2017/4/12                                           | 2021/8/6                                           |

| Topic<br>Cluster             | Operation                                        | Operation                                                 | Component                                           | Component                                          |

| Keyterms                     | read/write data<br>page/plane<br>control circuit | redundancy scheme<br>access request<br>connect/disconnect | analog sensing<br>threshold voltage<br>read voltage | NAND strings<br>voltage regulator<br>erase voltage |

| Combined<br>Patent<br>Impact | 2.43                                             | 3.86                                                      | 11.36                                               | 2.07                                               |

| Assignees                    | SANDISK CORP.                                    | SAMSUNG<br>ELECTRONICS CO<br>LTD                          | QORVO                                               | SANDISK CORP.                                      |

Table 5. Cluster 1 non-citation patents.

The non-citation patents of cluster 2 are shown in Table 6. Judging from the combined patent impact index, US11114164B2 has the highest score. This patent discloses the method of adaptive write operations for non-volatile memories. The method includes multiple column voltage and multiple lines.

|                              | US20180157616A1                                            | GB2536309A                                         | KR1757159B1                                                                         | US11114164B2                     |

|------------------------------|------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------|

| Application<br>Date          | 2018/2/2                                                   | 2015/5/11                                          | 2017/7/12                                                                           | 2021/9/7                         |

| Topic<br>Cluster             | Application                                                | Application                                        | Communication                                                                       | Application                      |

| Keyterms                     | clock gating unit,<br>system-on-chip,<br>bus bridge device | clock signal,<br>bidirectional bus<br>master/slave | control area<br>network, public<br>address<br>broadcasting, time<br>synchronization | column voltage,<br>column line,  |

| Combined<br>Patent<br>Impact | 4.22                                                       | 1.36                                               | 1.36                                                                                | 5.29                             |

| Assignees                    | SAMSUNG<br>ELECTRONICS<br>CO LTD                           | CIRRUS LOGIC<br>INC.                               | KIM JONG UN                                                                         | SAMSUNG<br>ELECTRONICS<br>CO LTD |

Table 6. Cluster 2 non-citation patents.

The non-citation patents of cluster 3 are shown in Table 7. Judging from the combined patent impact index, US20120144078A1 has the highest score. This patent claims a single wire bus architecture. This architecture includes a single wire bus, slave devices, master devices, and the communication protocols are described in the patent as well.

Table 7. Cluster 3 non-citation patents.

|                              | US20120144078A1                                   | US20120198266A1                                      | US20130031284A1                                            | US20200050571A1                                                    |

|------------------------------|---------------------------------------------------|------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------|

| Application<br>Date          | 2010/12/2                                         | 2011/1/28                                            | 2012/7/24                                                  | 2019/10/17                                                         |

| Topic<br>Cluster             | Structure                                         | Technique                                            | Structure                                                  | Structure                                                          |

| Keyterms                     | wire bus,<br>clock signal,<br>master/slave device | Interconnect bus,<br>master/slave port,<br>bandwidth | bus bridge system,<br>clock gating unit,<br>system-on-chip | multi-drop bus,<br>receive/issue,<br>peer-to-peer<br>communication |

| Combined<br>Patent<br>Impact | 38.53                                             | 20.3                                                 | 10.29                                                      | 8.51                                                               |

| Assignees                    | BLACKBERRY<br>LTD.                                | QUALCOMM INC                                         | SAMSUNG<br>ELECTRONICS<br>CO LTD                           | INTEL<br>CORPORATION                                               |

# 5. Conclusion

This paper, derived from two patent infringement lawsuits, demonstrates practical applications of integrated patent analysis: (i) identifying essential and extended patents related to the litigations based on the key component of the claims; (ii) performing K-means clustering and Latent Dirichlet Allocation (LDA) to identify patent collections into six groups exclusively and non-exclusively; (iii) conducting radar analysis of competitive technologies among leading companies.

The context of patents might appear to be different because of the terms used. But in reality, they may be similar in the technical fields and origins. As a result, patent similarity comparison analysis will generate better results with the help of additional ontology exploration. This paper differs from previous studies is to define an ontology schema as a knowledge graph of key domains based on topic clustering results, which requires essentially a transdisciplinary knowledge engineering. Thus, the semantics of patents in different technology fields can be understood and ontology constructed for conducting meaningful similarity analysis. This research also extract and capture the relationships between major technology classes through radar analysis. Patent filing trends provide additional insights into the related technologies in the industry, which also reflect the patenting landscapes. Patent-based technology mining can facilitate advanced strategic R&D and patent management.

As the concluding remarks, this research breaks down the well-known semiconductor infringement case into two parts. Firstly, this research collects comprehensvie patents based on the keywords of two infringement-related patents. The patent collections are used to analyze patenting trends, essentially by the top 5 assignees. They are also used to analyze the top 5 IPC-classes' patents of these assignees. By doing so, the unique competitive advantages of firms and their core competences can be better identified. Secondly, K-means clustering and LDA are conducted to divide patents into groups. This research narrows down the top 2 patents in each group without citation records. Judging by the increasingly common patent litigations, the uncited patents in given fields are closely monitored for IP protection.

# Acknowledgment

This research is partially supported by the Ministry of Science and Technology (Taiwan) individual research grants (Grant numbers: MOST-110-2221-E-007-113-MY3 and MOST-108-2221-E-007-075-MY3).

#### References

- Mckay drive.VLSI Technology, Inc, 2021, Company Profile, Information, Business Description, History, Background Information on VLSI Technology, Inc, https://www.referenceforbusiness.com/history2/80/VLSI-Technology-Inc.html, accessed: 27. 10. 2021.

- [2] M.J. Berry and G.S. Linoff, Data mining techniques: for marketing, sales, and customer relationship management, John Wiley & Sons, Hoboken, 2004.

- J. Sun, J. Liu and L. Zhao, Clustering algorithms Research, *Journal of Software*, 2008, Vol. 19(1), pp. 48-61.

- [4] A. J. Trappey, C.V. Trappey and A.C Chang, Intelligent extraction of a knowledge ontology from global patents: The case of smart retailing technology mining, *International Journal on Semantic Web and Information Systems (IJSWIS)*, 2020, 16(4), pp. 61-80.

- [5] Eet news, 1997, *Philips Acquires VLSI Technology with Raised Bid*, https://www.eetimes.com/philips-acquires-vlsi-technology-with-raised-bid/, accessed: 03.05.1997.

- [6] Ivy Bridge, 2021, Microarchitectures Intel WikiChip. (n.d.), https://en.wikichip.org/wiki/intel/microarchitectures/ivy\_bridge\_(client), accessed: 20.10.2021.

- [7] C.V. Trappey, A.J. Trappey and C.Y. Wu, *Clustering patents using non-exhaustive overlaps. J. Syst. Sci. Syst. Eng.* 2010, 19, 162–181, https://doi.org/10.1007/s11518-010-5134-x.