Smart Intelligent Computing and Communication Technology V.D. Ambeth Kumar et al. (Eds.) © 2021 The authors and IOS Press. This article is published online with Open Access by IOS Press and distributed under the terms of the Creative Commons Attribution Non-Commercial License 4.0 (CC BY-NC 4.0). doi:10.3233/APC210087

# Low Power, High Speed MUX Based Area Efficient Dadda Multiplier

Kalaiyarasi.D<sup>a,1</sup>, Pritha.N<sup>b</sup>, Srividhya.G<sup>b</sup>, Padmapriya.D<sup>b</sup>

<sup>a</sup>Associate Professor, Dept of ECE, Panimalar Engineering College, Chennai, India <sup>b</sup>Associate Professor, Dept of ECE, Panimalar Engineering College, Chennai, India

Abstract. The multiplier is a fundamental building block in most digital ICs' arithmetic units. The multiplier architecture in modern VLSI circuits must meet the main parameters of low power, high speed, and small area requirements. In this paper, a 4-bit multiplier is constructed using the Dadda algorithm with enhanced Full and Half adder blocks to achieve a smaller size, lower power consumption, and minimum propagation delay. The Dadda Algorithm-designed multiplier is used in the first phase to reduce propagation delay while adding partial products in three stages provided by AND Gates. In the second phase, each stage of the Dadda tree algorithm is built with an enhanced Full and half adders to reduce the design area, propagation delay, and power consumption while still meeting the requirements of the current scenario by using MUX logic. In an average of Conventional array Multipliers, the proposed Dadda multiplier achieved an 84.68 % reduction in delay, 70.89 % reduction in power, 84.68% increase in Maximum Usable Frequency (MUF), and 95.55% reduction in Energy per Samples (EPS).

Keywords. 4\*4 multiplier, Dadda algorithm, Enhanced Full and Half adder, MUX logic

### 1. Introduction

The multiplier is used in a variety of applications, including VLSI design, signal processing, digital communication, and electronics. In the current scenario, low power, high speed, and a small area are important. Multipliers with the least delay and power dissipation are chosen in order to achieve optimal throughput and device response when designing an optimal circuit. The Dadda Algorithm multiplier architecture operates at a high frequency and consumes comparatively less power, as well as magically reducing power consumption, which leads to the concept of using it in larger circuits where multipliers play a major role [11-12]. The Dadda Algorithm-designed multiplier is used in the first phase and MUX logic in the second phase, each stage of the Daddatree algorithm is built with an enhanced Full adder and half adder to further reducethe design area, propagation delay, and power dissipation. This paper has sevensections. Multiplier with an existing method is presented in Section II, proposed research is described in Section III, block diagrams and algorithm implementation are

<sup>&</sup>lt;sup>1</sup>Kalaiyarasi.D, Associate Professor, Dept of ECE,PanimalarEngineeringCollege,Chennai,India. Email: kalaiccarthi@gmail.com

presented in Section IV and V, simulation and implementation results are listed in Section VI, and the conclusion is in Section VII.

## 2. Previous Research

Many algorithms named Wallace tree [1-2], Vedic and Booth algorithms [3] were used in previous research to achieve optimized power and delay product. To reduce the area and latency, a booth encoding method was used in conjunction with a compressor [4]. Furthermore, to minimize switching operation, partial products [5] are reordered to reduce power consumption. In the reduction power, a modified full adder with 4:1 multiplexers is used, and a full adder with six 2:1 multiplexers is also designed. The digital design with low power dissipation and minimal delay, as well as maximum throughput and high speed can be achieved byvarious techniques such as merged delay transformation [6], genetic algorithm [7], evolutionary algorithm [8], delay path Unequalization [9], carry-look-ahead logic [10], etc.

## 3. Proposed Research

To achieve less area, low power consumption, and minimal propagation delay, a 4-bit multiplier is constructed using the Dadda algorithm and enhanced Half and Full adder blocks in the proposed work. The multiplier built in the first phase with the Dadda algorithm was used to reduce the propagation delay. By using multiplexer logic, a multiplier built in the second phase uses enhanced Full adder and half adder to further reduce the design area, propagation delay, and power dissipation. Area is saved as a result of the above two steps, and propagation delay is magically reduced.

## 3.1 Introduction to Dadda Tree Algorithm

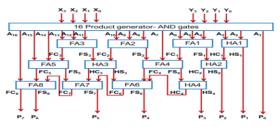

A 4\*4 multiplier has 16 partial products, the tree's height is four. The Dadda Algorithm was used to reduce the tree's height from four to two levels. Since the simulation of the next stage does not need to wait for carry from the previous stage, the Dadda Algorithm is ideal for reducing the overall multiplier design delay.

## 3.2 Dadda Algorithm Stages

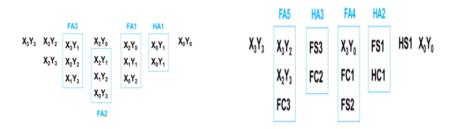

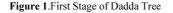

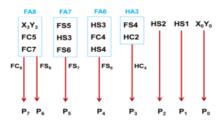

The aim of the algorithm is to reduce the tree's height from four to two. The height of the tree is reduced from four to three in the first stage and from three to two in the second stage of the Dadda algorithm. By using ripple carry adders in the third stage of the Dadda algorithm, the tree's height is limited to two. To reduce this tree, the first two Dadda stages are used. The Dadda phases are depicted in Figs. 1, 2, and 3.

Figure 2. Second Stage of Dadda Tree

Figure 3. Third Stage of Dadda Tree

#### 3.3Algorithm Implementation

To minimize the height of the tree from four to three, a half adder is added to the second column, a full adder to the fourth column, and two full adders to the third and fifth columns. To reduce the height of the tree from three to two, two half adders are applied to the third and fifth columns, and two full adders are applied to the fourth and sixth columns in the second level. In the final step, ripple carryadders are used to confine the multiplication results. Parallel processing of half adders and full adders, where each adder works independently and does not wait for carry from the previous level, will increase the efficiency of the implementation.

#### 4. Architecture of Proposed Dadda Multiplier

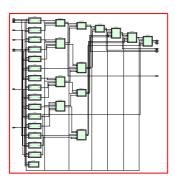

The block diagram of Proposed Dadda multiplier is shown in Fig. 4.

Figure 4.Block Diagram of Proposed Dadda Multiplier

## 5. Building Blocks of Proposed Multiplier

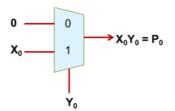

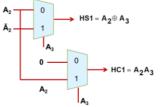

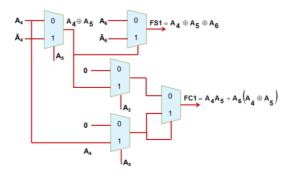

The MUX-based enhanced AND gate, enhanced half adder and enhanced full adder are shown in Fig.5,6 and 7 respectively.

Figure 5. Proposed AND gate using 2:1 MUX

Figure6. Proposed HA using 2:1 MUX

Figure 7. Proposed FA using 2:1 MUX

## 6. Implementation Results

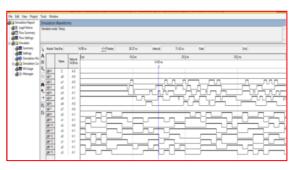

This section describes the implementation results of a four-bit multiplier based on the Dadda algorithm, as well as enhanced full and half adders. Using Altera Quartus II and the EP2S15F484C3 device, a four-bit multiplier design is developed and simulated. Table 1 shows the design, implementation, and analysis of a multiplier using enhanced full adders and half adders, as well as their performance parameters. The RTL view, Chip layout and simulation output of the proposed multiplier are shown in Fig.8, Fig.9and Fig.10, respectively. The proposed Dadda multiplier with enhanced full adder and half adder achieved 84.68% reduction in delay, 70.89% reduction in power consumption, 84.68% increase in Maximum Usable Frequency (MUF), and 95.55% reduction in Energy per Samples (EPS).

Figure 8.RTL View of Proposed design

Figure 9. Chip layout of proposed design

Figure 10. Simulation Output of Proposed Design

Table 1. Performance Comparison

| Multiplier Type                                 | Delay(ns) | Power(mW) | MUF (MHz) | PS (ns x mW) |

|-------------------------------------------------|-----------|-----------|-----------|--------------|

| Multiplier using<br>Conventional Full<br>Adder  | 49.98     | 2.197     | 20.00     | 109.8        |

| Multiplier using<br>4:1 MUX based<br>Full Adder | 49.09     | 5.592     | 20.37     | 274.5        |

| Multiplier using<br>2:1MUX based<br>Full Adder  | 49.57     | 1.218     | 20.17     | 60.37        |

| Proposed Dadda<br>Multiplier using<br>2:1 MUX   | 7.588     | 0.6       | 131.78    | 4.5528       |

## 7. Conclusion

The proposed 4 bit multiplier design has been developed, and the schematics have been simulated using Altera Quartus II and the EP2S15F484C3 unit. The schematic for the

Dadda tree algorithm is shown, which includes an AND gate with a 2:1 MUX, a half adder with two 2:1 MUX, and a full adder with four 2:1 MUX. The output parameters are compared to those of current full adder array multipliers. As the proposed design incorporates the Dadda algorithm to minimize propagation delay and the number of stages or area of the multiplier, it is implemented efficiently. Furthermore, by enhancing the full adder and half adder in each stage of the Dadda tree algorithm, in an average of Conventional array Multipliers, the proposed Dadda multiplier achieved an 84.68 % reduction in delay, 70.89 % reduction in power, 84.68% increase in MUF, and 95.55% reduction in EPS.

#### References

- [1] Wallace.A suggestion for a fast multiplier. IEEE Transaction on Electronic Computers, Vol. EC-13, pp.14-17.

- [2] ShahzadAsif and Yinan Kong .Low Area Wallace Multiplier, VLSI Design. vol. 2014.

- [3] Rao.M.J , Dubey.S .A high speed and area efficient Booth recoded Wallace tree multiplier for Fast Arithmetic Circuits. in Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), Hyderabad, India, 5-7 Dec. 2012, pp.220-223.

- [4] Karthick, S. Karthika and S. Valannathy, Design and Analysis of Low Power Compressors, International Journal of Advanced Research in Electrical, Electronics and instrumentation Engineering, YoU, Issue 6, Dec. 2012.

- [5] S.T.Oskuii,P.G.Kjeldsberg,Power optimized partial product reduction interconnect ordering in parallel multipliers, NORCHIP, Aalborg,19-20 Nov.2007,pp.1-6.

- [6] Design of high-speed carry saves adder using carry look ahead adder. Available from: https://www.researchgate.net/publication/301407573\_Design\_of\_high\_speed\_carry\_save\_adder\_using carry lookahead adder [accessed Sep 22, 2017].

- [7] PremKumar.P, Duraiswamy.K and JoseAnand.A. An optimized devicesizing of analog circuits using genetic algorithm, European Journal of Scientific Research, vol.69, no.3, pp.441–448,2012.

- [8] RevnaAcarVural, Member, IEEE, BurcuErkmen, Member, IEEE, UfukBozkurt, TulayYildirim, Member, IEEE, CMOS Differential Amplifier Area Optimization with Evolutionary Algorithms, Proceedings of the World Congress on Engineering and Computer Science 2013 Vol II WCECS 2013, 23-25 October, 2013, San Francisco, USA.

- [9] Jorge Juan Chico, Enrico Macii, book chapter 17, Power- Consumption Reduction in Asynchronous Circuits Using Delay Path Unequalization, page (151-160), 13th International Workshop, PATMOS 2003 Turin, Italy, September 10-12, 2003, Proceedings.

- [10] RaminderPreet Pal Singh, Parveen Kumar, Balwinder Singh, Performance Analysis of 32 bit Array Multiplier with Carrying Save Adder and with Carry Look ahead adder, in International Journal of Recent Trends in Engineering, Vol 2, No. 6, November 2009

- [11] Bharathi.S.L, Pritha.N, Srividhya.G, PadmaPriya.D .A Frame of Multiplier using Compactor. Int Journal of Innovative Science and Research Technology, ISSN: 2456-2165, Vol. 3 Issue 3, March – 2018.

- [12] Kalaiyarasi.D and Saraswathi.M.Design of an Efficient High Speed Radix-4 Booth Multiplier for both Signed and Unsigned Numbers. International Conference on Advances in Electrical, Electronics, Information, Communication and Bio-Informatics (AEEICB) 27-28 Feb. 2018, IEEE 2018.